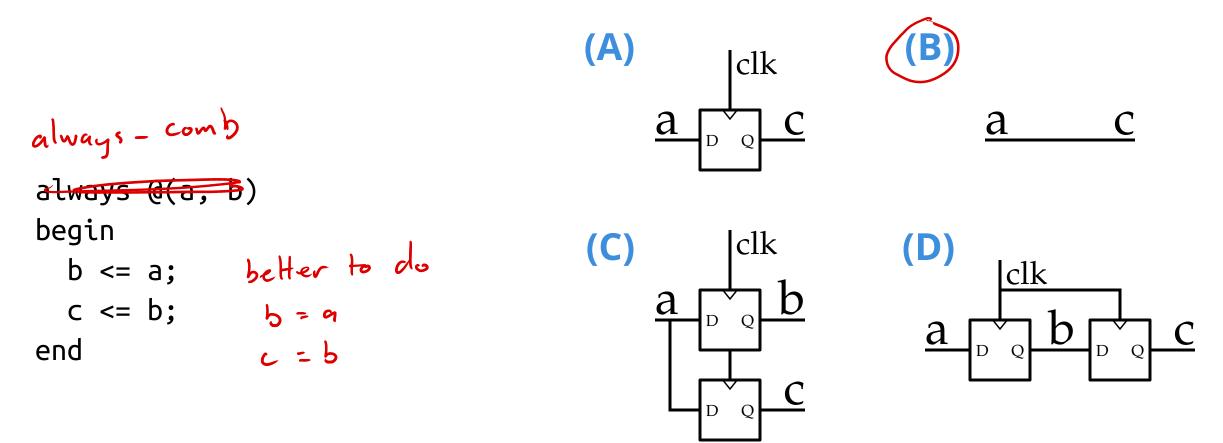

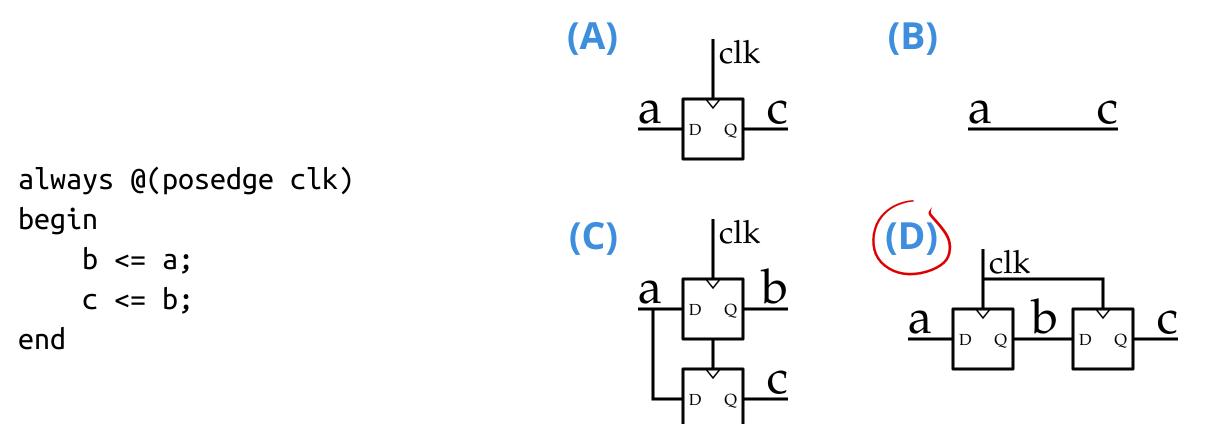

Which circuit will be created by the SystemVerilog below?

Which circuit will be created by the VHDL below?

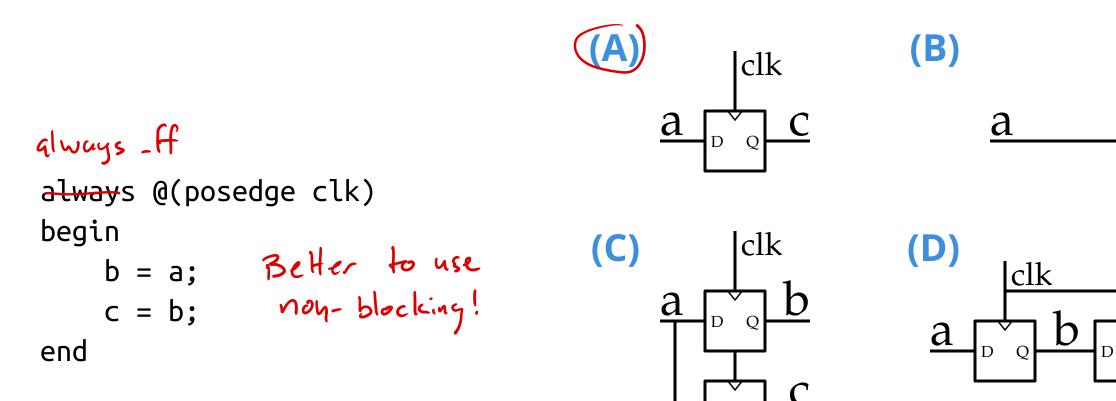

always \_ff

always @(posedge clk)

begin

c <= b;</pre>

end

0

D

SV

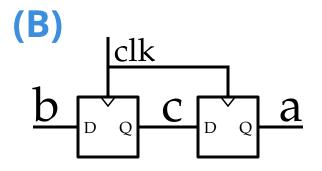

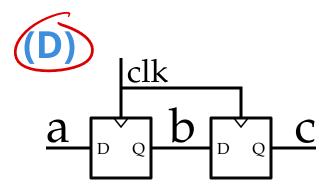

Which circuit will be created by the VHDL below?

Which circuit will be created by the VIID below?

SJ

Which circuit will be created by the  $\forall HD$  below?

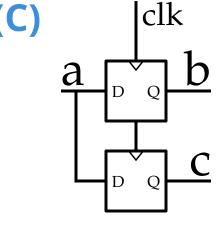

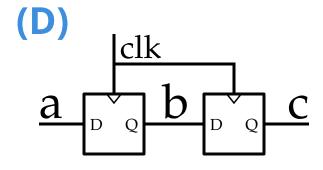

assign c = b; always @(posedge clk) begin

end

b (= a; c (= a;

clk

SV

a

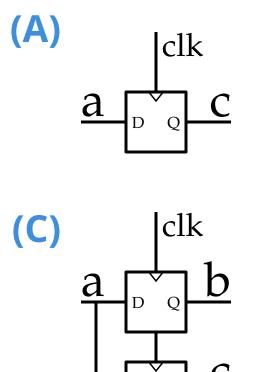

**(B)**

a

same behavior

# **EE 201:** State machines, part 1

Steven Bell 29 February 2024

# Objectives

- Explain what a state machine is

- Explain the difference between a Mealy and Moore state machine

- Given an English description of a system:

- Draw the state diagram

- Determine how many bits of state are necessary,

- and choose state encodings

- Write logic equations for the state transitions and outputs

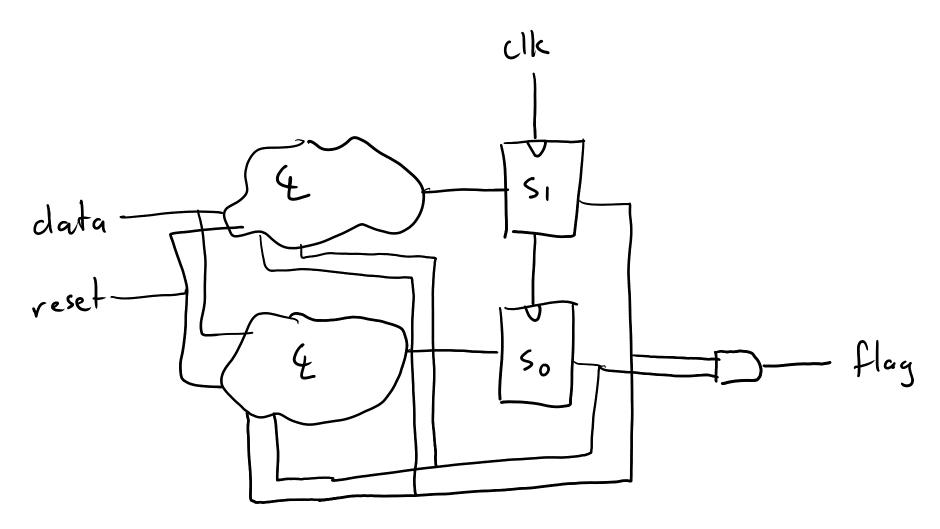

- Draw the complete logic circuit diagram for the FSM

# What good are state machines?

State machines are a *way of thinking* about digital logic problems

State machines let us build circuits that can perform sequences of actions and make decisions.

Complex behavior can be decomposed into discrete states, and possible actions in each state.

#### Where do we use FSMs?

Toy examples to torment digital logic students

Creating decision-making or sequential behavior

Detecting patterns (e.g., DFAs for parsing)

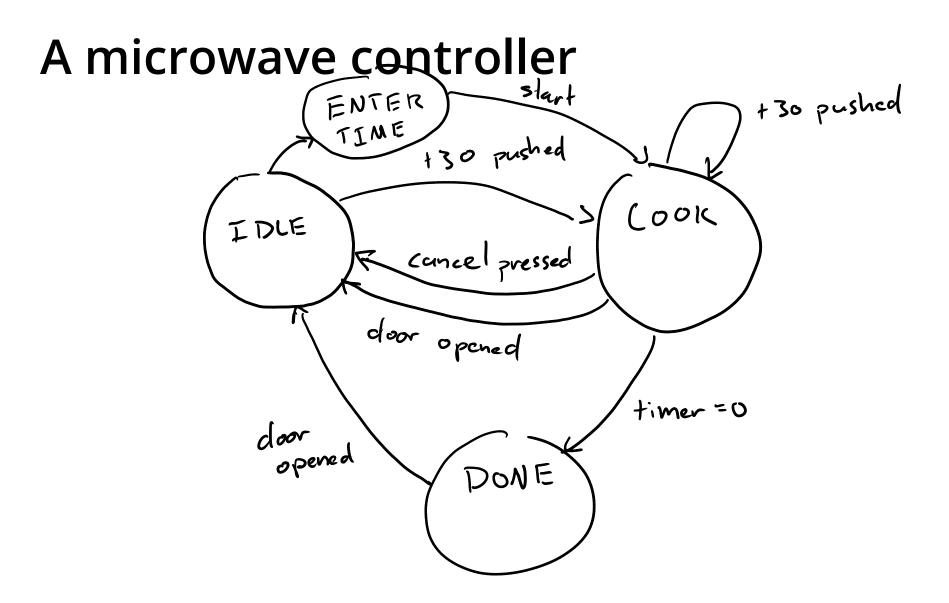

# Defining the problem

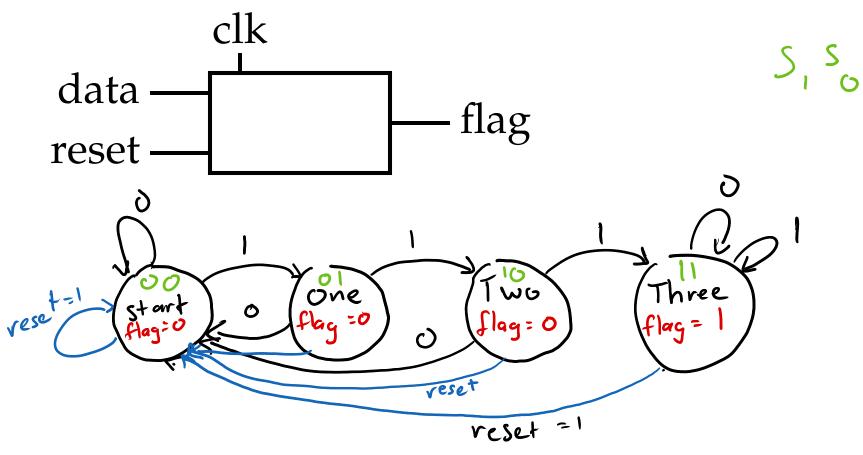

Design a circuit which sets a flag high when the "data" input has been high for 3 clock cycles in a row. The flag should stay high until the reset signal is asserted (i.e., = 1)

# Side note: Graphviz is awesome

Graphviz provides a language for describing graphs (like FSMs) and can draw them automatically.

Experiment at edotor.net

It's also installed on the Halligan servers (run **dot** --help) **dot** -Tpng -oFILENAME INPUTFILE.GV

| Putting it all together |   |    |       |      |     |        |                                                       |

|-------------------------|---|----|-------|------|-----|--------|-------------------------------------------------------|

|                         | S | SG | reset | data | Nex | it sta |                                                       |

|                         | 0 | 0  | 0     | Θ    | 0   | 0      | 5, 50<br>0° 01 1' 10                                  |

| start                   | 0 | Θ  | Θ     | 1    | S   | ι ι    | 000000000                                             |

|                         | 0 | Θ  | 1     | Θ    | 0   | 0      |                                                       |

|                         | 0 | Θ  | 1     | 1    | G   | U      | reset, data 10010                                     |

|                         | 0 | 1  | Θ     | Θ    | 6   | 0      | 100000                                                |

| onl                     | 0 | 1  | Θ     | 1    | t   | Э      | 10 0 0 0 0                                            |

|                         | 0 | 1  | 1     | Θ    | C   | 0      | 10 0 0 0 0                                            |

|                         | 0 | 1  | 1     | 1    | 0   | 0      |                                                       |

|                         | 1 | 0  | Θ     | Θ    | C   | 0      | reset data So + reset S, So                           |

| two                     | 1 | Θ  | Θ     | 1    | ۱ I |        |                                                       |

|                         | 1 | Θ  | 1     | Θ    | U   | Ο      |                                                       |

|                         | 1 | Θ  | 1     | 1    | O   | 0      | S, So flog                                            |

|                         | 1 | 1  | 0     | Θ    | t   | l      |                                                       |

| three                   | 1 | 1  | 0     | 1    | ι   | 1      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

|                         | 1 | 1  | 1     | 0    | C   | 0      | 0 0                                                   |

|                         | 1 | 1  | 1     | 1    | O   | 0      |                                                       |

# Putting it all together

#### Moore vs Mealy

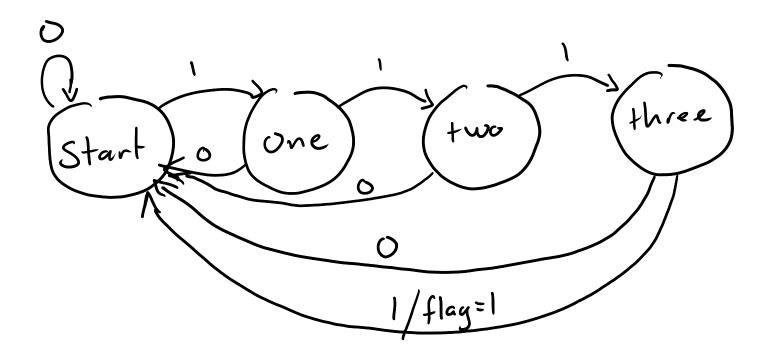

Tweak our previous example: detect four 1s in sequence, and go back to the reset state automatically.

#### Moore vs Mealy

Book example: Alyssa's robot snail smiles when it detects "01"

# What else is a state machine?

Every sequential circuit can be considered a state machine. Sometimes this is helpful, sometimes not.

#### For next time

- 1. No new reading!

- 2. Paper HW #2 posted, due Thursday 3/7