# **EE 201:** Sequential logic timing

#### Steven Bell 7 March 2024

#### INTRODUCTION TO DIGITAL LOGIC

Computer Programming

Memory

Verilog

PROCESS BLOCK PERILS

VHDL

Swamps of Arcane Syntax

----- FLIP-FLOP PASS

FIELDS OF

Plains of Combinational Logic

Desert of Management of "How things used to be done"

ENGLIGHTENMENT SEQUENTIAL LOGIC YOU ARE HERE

STATE MACHINES

Computer Architecture

# By the end of class today, you should be able to

- Define setup time and hold time, and annotate them on a timing diagram

- Take a sequential circuit and a table of gate/FF delays, and draw a timing diagram.

- Calculate the **maximum frequency** a circuit can run at

- Calculate whether a circuit will have a hold time violation

- Optimize sequential circuits for speed, using spatial and temporal parallelism

- Explain what **metastability** is, and how to reduce it

## Terms

### Clock-to-Q propagation delay (t<sub>pcq</sub>)

Propagation delay from rising edge of clock to new value at Q

### Setup time

Time before clock edge that FF needs to set up; input must be stable at least this much **before** clock edge.

#### Hold time

Time after clock edge that FF needs value to hold still; input must be stable at least this much **after** clock edge.

# Clock-to-Q propagation delay $(t_{pcq})$

Propagation delay from rising edge of clock to new value at Q

#### Setup time

Input must be stable at least this much **before** clock edge.

tpc

Q = D

new Q value

#### Hold time

Input must be stable at least this much **after** clock edge.

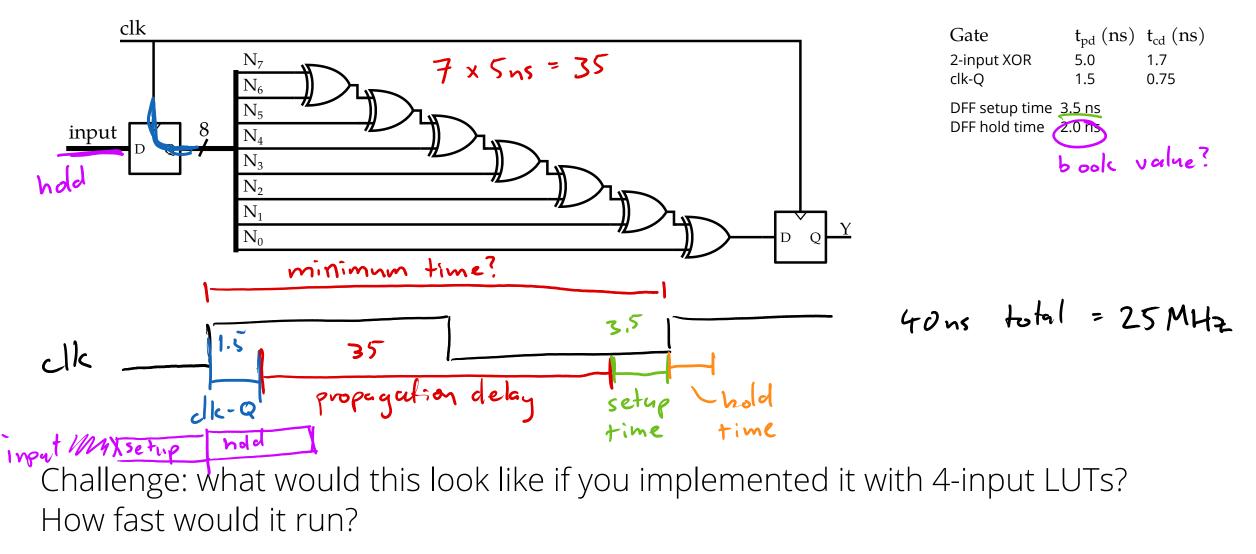

# How fast can this run?

(i.e., what is the maximum clock frequency before timing failure?)

Don't we care about time to result?

# How fast can this run?

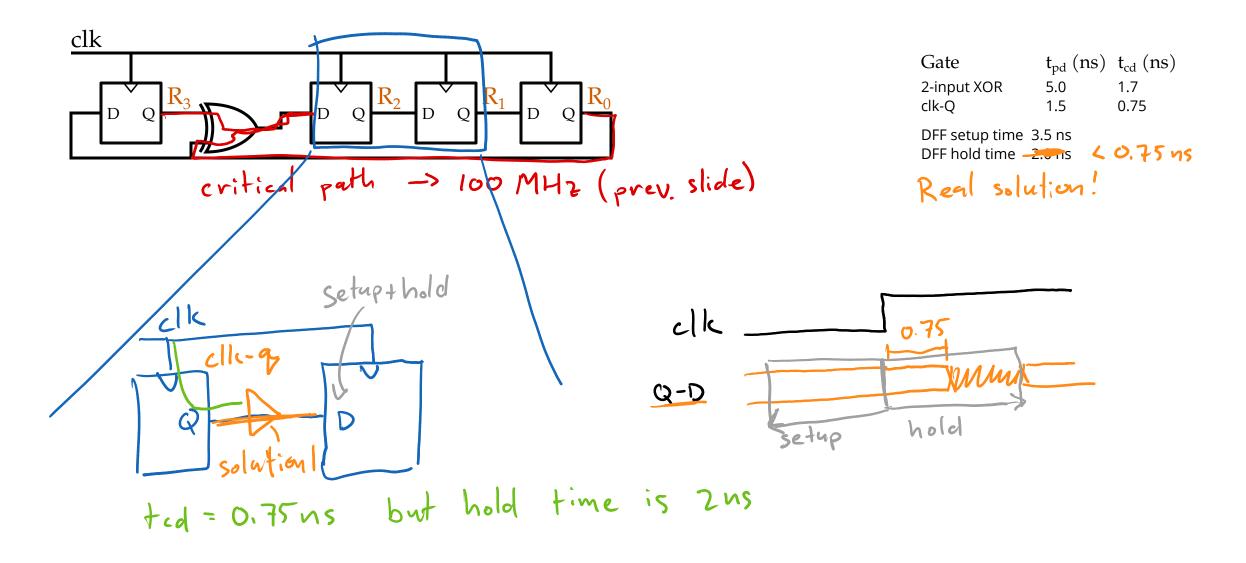

| Gate           | $t_{pd} (ns)$ | $t_{cd}$ (ns) |

|----------------|---------------|---------------|

| 2-input XOR    | 5.0           | 1.7           |

| clk-Q          | 1.5           | 0.75          |

| DFF setup time | 3.5 ns        |               |

| DFF hold time  | 2.0 ns        |               |

# Can this run at 75 MHz?

Those equations look pretty complicated; do we have to memorize them?

### Those equations look pretty complicated; do we have to memorize them?

#### Please don't.

You'll make your head hurt, do poorly on the exam, and forget all of it two months from now.

# How do we speed this up? 25 MHz

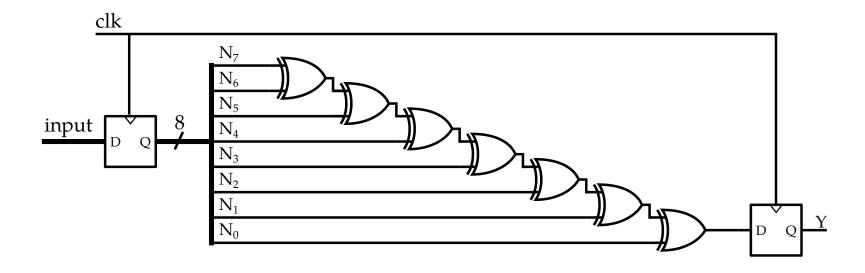

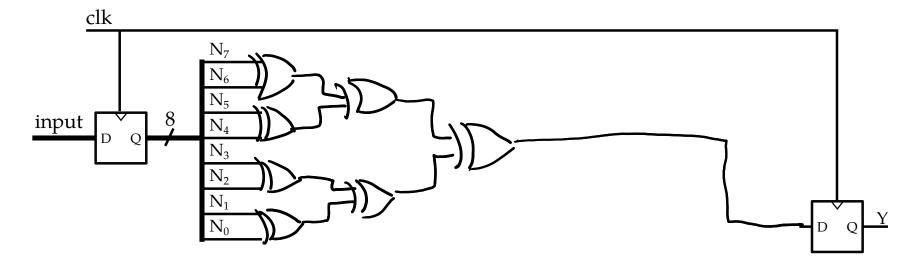

# Speeding up the XOR circuit $15 + 3 \times 5 = 15$

+ 3.5 = 20 ns = 50 MHz

# Other ways to speed up the circuit?

# Other ways to speed up the circuit?

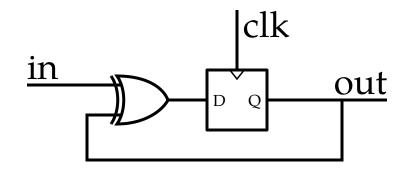

# Metastability

What happens if a flip-flop input (D) isn't a stable low or high value? The digital abstraction is broken!

# But how would that happen?

1) An external input is giving your circuit a non-digital voltage

2) There is a setup time violation

3) You have a digital input from an external source

4) You have more than one clock in your design

# But how would that happen?

1) An external input is giving your circuit a non-digital voltage Don't do that, silly!

2) There is a setup time violation Run slower / fix your design to meet timing

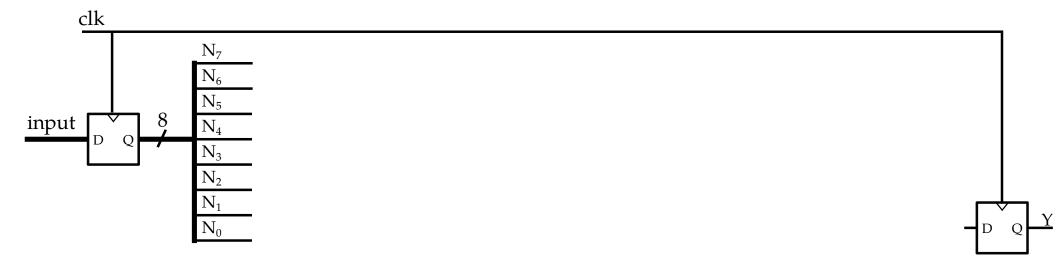

3) You have a digital input from an external source Use a synchronizer

4) You have more than one clock in your design

# Does metastability actually matter to me?

Yes, you may see it on your FPGA!

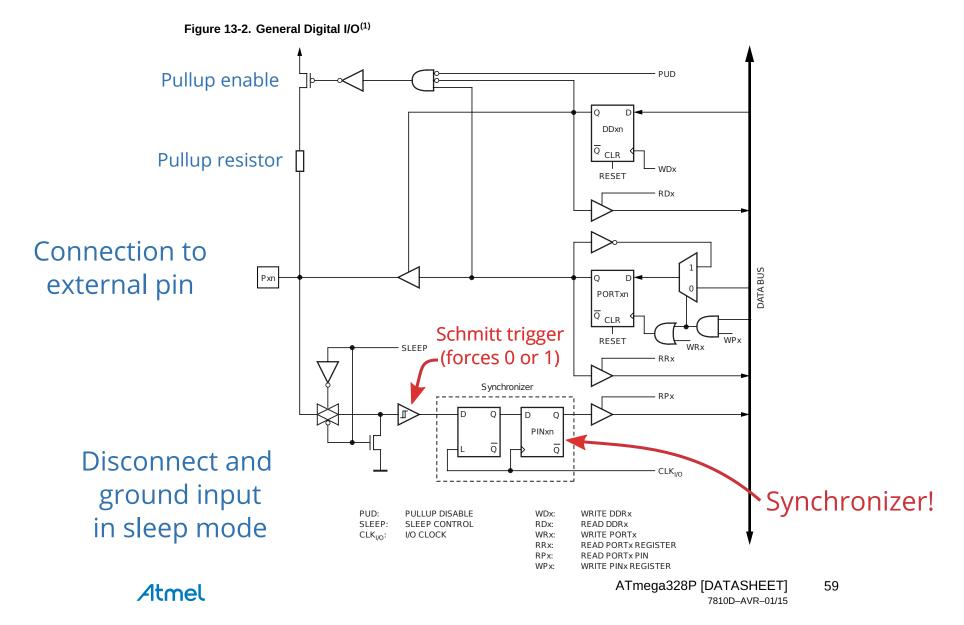

# Metastability in practice: inside an Arduino pin